ѕ©ґЙѕ§Хс,УРФґѕ§Хс,KC5032E-C3ѕ§Хс,УРФґѕ§Хс,КЗЦ»ѕ§Ме±ѕЙнЖрХсРиТЄЁuНвІїµзС№№©У¦,ЖрХсєуЁЊїЙЦ±ЅУЗэ¶ЇCMOS јЇіЙµзВ·,ІъЖ·±ѕЙнТСКµПЦУл±ЎРНICЈЁTSSOP·вЧ°,TVSOP·вЧ°Ј©Н¬СщµД1mmєс¶И,¶ПїЄК±µДПыЎб·СµзБчКЗ15 µAТФПВ,±аґш°ьЧ°·ЅКЅїЙ¶ФУ¦¦ЖЎЎЧФ¶ЇґоФШј°IR»ШБчєёЅУЈЁОЮЗ¦¶ФУ¦Ј©ІъЖ·УРјёЦЦµзС№№©СЎ1.8V,2.5V,3V3.3V,5V,ТФУ¦¶ФІ»Н¬ICІъЖ·РиТЄ

єгОВѕ§ХсµДХжЎ»їХ·вЧ°јјКхЈєКЗЦёКЇУўѕ§ХсФЪХжїХ·вЧ°ЗшУтДЪЅшРР·вЧ°ЎЈ1.·АЦ№НвЅзЖшМеЅшИлЧйјюМеДЪКЬµЅОЫИѕєНФцјУУ¦Б¦µДІъЙъЈ»2.К№ѕ§Хс¦жЧйјюФЪХжїХПВµзЧијхРЎЈ»3.ЖшГЬРФёЯЎЈґЛјјКхОЄСР·ўј°ЙъІъі¬РЎРНЎўі¬±ЎРНКЇУўѕ§Хс±ШР빥їЛµД№ШјьјјКхЦ®Т»

|

ПоДї |

·ыєЕ |

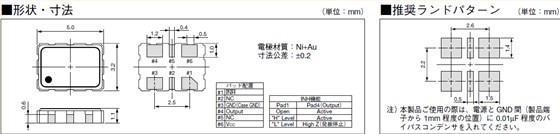

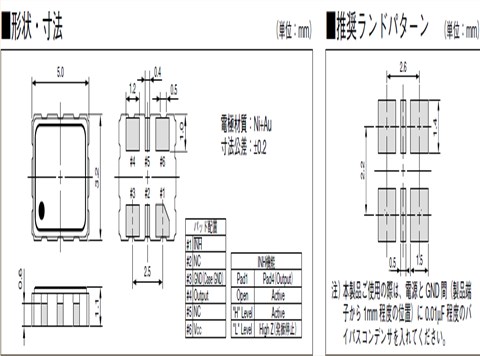

№жёсЛµГч |

Мхјю |

|

КдіцЖµВК·¶О§ |

f0 |

14.31818-166MHz |

ЗлБЄПµОТГЗТФ±г»сИЎЖдЛьїЙУГЖµВКµДПа№Ш©IЎЎРЕПў |

|

µзФґµзС№ |

VCC |

2.97-3.63 V |

ЗлБЄПµОТГЗТФБЛЅвёь¶аПа№ШРЕПў |

|

ґўґжОВ¶И |

T_stg |

-55Ўжto +125Ўж |

Вгґж |

|

№¤ЧчОВ¶И |

T_use |

-10Ўжto +70Ўж |

ЗлБЄПµОТГЗІйїґёь¶аЁЋЧКБПhttp://www.yijindz.com |

|

|

|||

|

|

|||

|

ЖµВКОИ¶Ё¶И |

f_tol |

J: ±50 × 10-6 |

|

|

L: ±100 × 10-6 |

|||

|

T: ±150 × 10-6 |

|||

|

№¦єД |

ICC |

3.5 mA Max. |

ОЮёєФШМхЁЂјюЎўЧоґу№¤ЧчЖµВК |

|

ґэ»ъµзБч |

I_std |

3.3¦МA Max. |

ST=GND |

|

ХјїХ±И |

SYM |

45 % to 55 % |

50 % VCC ј«, L_CMOSЁQ15 pF |

|

КдіцµзС№ |

VOH |

VCC-0.4V Min. |

|

|

VOL |

0.4 V Max. |

|

|

|

КдіцёєФШМхјю |

L_CMOS |

15 pF Max. |

|

|

КдИлµзС№ |

VIH |

80% VCCMax. |

STЦХ¶Л |

|

VIL |

20 % VCCMax. |

||

|

ЙПЙэ/ПВЅµК±јд |

tr / tf |

4 ns Max. |

20 % VCCto 80 % VCCј«, L_CMOS=15 pF |

|

ХсЎюµґЖф¶ЇК±јд |

t_str |

3 ms Max. |

t=0 at 90 % |

|

ЖµВКАП»Ї |

f_aging |

±3 × 10-6/ year Max. |

+25 Ўж, іхДк¶И,µЪТ»Дк |

КЇУўѕ§ХсЧФ¶Ї°ІЧ°єНХжїХ»ЇТэ·ўµДіеЎФ»ч»бЖЖ»µІъЖ·МШРФІўУ°ПмХвР©ІъЖ·ЎЈЗлЙиЦГ°ІЧ°МхјюТФѕЎїЙДЬЅ«іе»чЅµЦБЧоµН,5032ѕ§…eМеХсµґЖчІўИ·±ЈФЪ°ІЧ°З°Оґ¶Фѕ§ХсМШРФІъЙъУ°ПмЎЈМхјюёД±дЎуК±,ЗлЦШРВјмІй°ІЧ°ЎьМхјюЎЈН¬К±,ФЪ°ІЧ°З°єу,ЗлИ·±ЈКЇУўѕ§ХсІъЖ·ОґЧІ»ч»ъЖч»тЖдЛыµзВ·…e°еµИЎЈ

Гїёц·вЧ°АаРНµДЧўТвКВПо

(1)МХґЙ°ьЧ°ѕ§ХсУлSONІъЖ·

ФЪєёЅУМХ¦· ґЙ·вЧ°ѕ§ХсєНSONІъЖ· (МХґЙ°ьЧ°КЗЦёѕ§ХсНв№ЫІЙУГМХґЙЦЖЖ·) Ц®єу,НдЗъµзВ·°е»бТт»ъРµУ¦Б¦¶шµјЦВєёЅУІї·Ц°юВд»т·вЧ°·ЦБСЈЁїЄБСЈ©ЎЈ6ЅЕУРФґХсµґЖчУИЖдФЪєёЅУХвР©ІъЖ·Ц®єуЅшРРµзЎЮВ·°еЗРёоК±,Ос±ШИ·±ЈФЪУ¦Б¦ЅПРЎµДО»ЦГІјѕЦѕ§МеўЩІўІЙУГУ¦Б¦ёьРЎµДЗРёо·Ѕ·ЁЎЈ

(2)МХґЙ°ь©IЧ°КЇУўѕ§Хс

ФЪТ»ёцІ»Н¬А©ХЕПµКэµзВ·°еЈЁ»·СхІЈБ§Ј©ЙПєёЅУМХґЙЎ··вЧ°КЇУўѕ§ХсК±,ФЪОВ¶Иі¤К±јдЦШёґ±д»ЇК±їЙДЬµјЦВ¶ЛЧУєёЅУІї·ЦЎр·ўЙъ¶ПБСЎы,ЗлКВПИјмІйєёЅУМШРФЎЈ

ЈЁ3Ј©ЦщГжКЅІъЖ·

ІъЖ·µДІЈБ§Ії·ЦЦ±ЅУНдЗъТэЅЕ»тУГБ¦АЙмТэЅЕЎј»бµјЦВФЪТэЅЕёщІї·ўЙъГЬ·вІЈБ§·ЦБСЈЁїЄБСЈ©,ТІїЙДЬµјЦВЖшГЬРФєНІъЖ·МШРФКЬµЅЖЖ»µЎЈ5032ѕ§МеХсµґЖчµ±УРФґѕ§ХсµДТэЅЕРиНдЗъіЙПВНјЛщКѕРОЧґК±,У¦ФЪХвЦЦіЎѕ°ПВБфіц0.5mmµДТэЅЕІўЅ«ЖдНРЧЎ,ТФГв·ўЙъ·ЦБСЎЈµ±ёГТэЅЕРи¦ШРЮёґК±,ЗлОрАЙм,НРЧЎНдЎбЗъІї·ЦЅшРРРЮХэЎЈФЪёГГЬ·вІї·ЦЙПК©јУТ»¶ЁС№Б¦,»бµјЦВЖшГЬРФКЬµЅЛрЁK»µЎЈЛщТФФЪґЛґ¦ЗлІ»ЎбТЄК©јУС№Б¦ЎЈБнНв,ОЄ±Ьёє»ъЖч№ІХсФміЙТэЅЕЖЈАНЗР¶П,ЅЁТйУГХіЧЕјБЅ«ІъЖ·№МФЪ¶ЁµзВ·°еЙПЎЈ

ѕ©ґЙѕ§Хс,УРФґѕ§Хс,KC5032E-C3ѕ§Хс

јУёЯѕ§Хс,УРФґѕ§Хс,HSO531SЛДЅЕМщЖ¬ѕ§Хс

јУёЯѕ§Хс,УРФґѕ§Хс,HSO531SЛДЅЕМщЖ¬ѕ§Хс